иљђиЗ™пЉЪhttp://www.ednchina.com/ART_8800501745_19_35499_AN_a996b8f4.HTM

OpenCLж†ЗеЗЖзЃАдїЛ

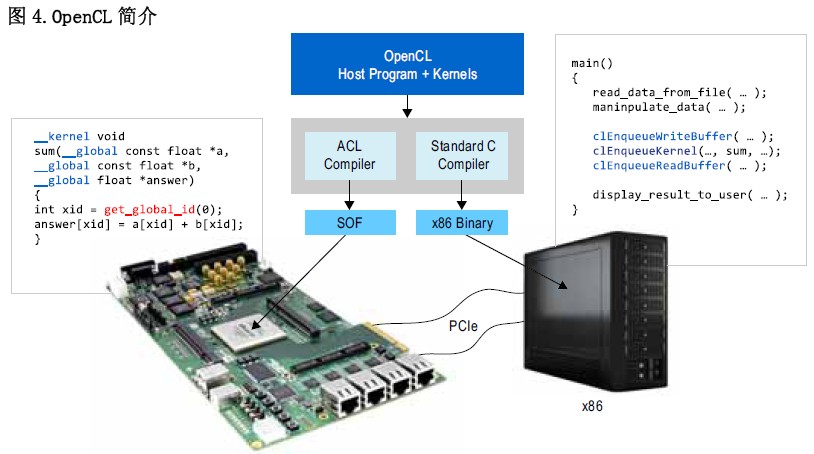

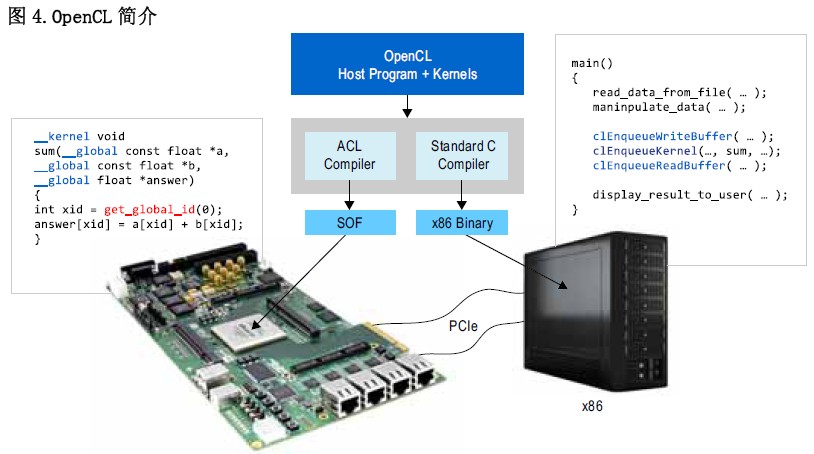

OpenCLеЇФзФ®з®ЛеЇПеРЂжЬЙдЄ§йГ®еИЖгАВOpenCLдЄїз®ЛеЇПжШѓзЇѓиљѓдїґдЊЛз®ЛпЉМдї•ж†ЗеЗЖC/C++зЉЦеЖЩпЉМеПѓдї•ињРи°МеЬ®дїїдљХз±їеЮЛзЪДеЊЃе§ДзРЖеЩ®дЄКгАВдЊЛе¶ВпЉМињЩз±їе§ДзРЖеЩ®еПѓдї•жШѓFPGAдЄ≠зЪДеµМеЕ•еЉПиљѓж†Єе§ДзРЖеЩ®гАБз°ђж†ЄARMе§ДзРЖеЩ®жИЦиАЕе§ЦзљЃx86е§ДзРЖеЩ®пЉМе¶ВеЫЊ4жЙАз§ЇгАВ

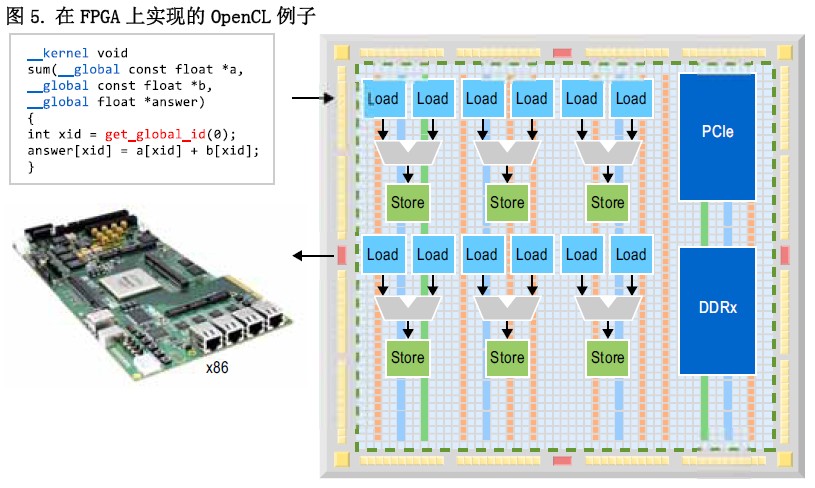

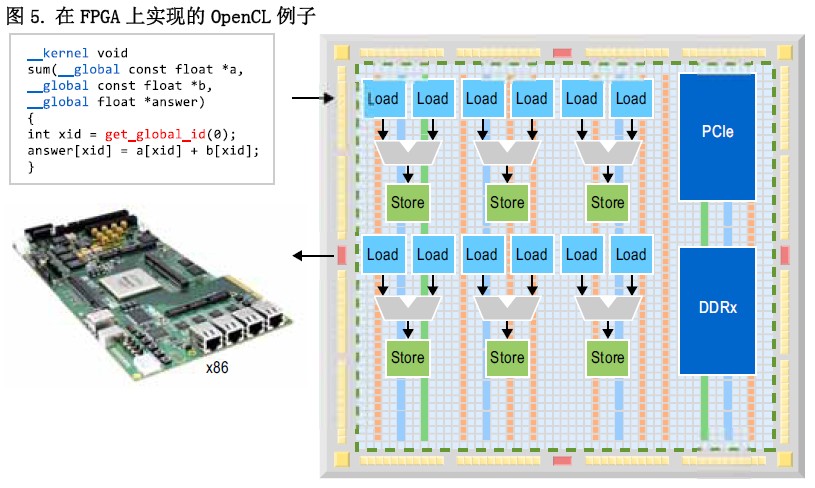

еЬ®ињЩдЄАдЄїиљѓдїґдЊЛз®ЛжЙІи°МжЬЯйЧізЪДжЯРдЄАзВєпЉМжЯРдЄАеКЯиГљжЬЙеПѓиГљйЬАи¶БеЊИе§ІзЪДиЃ°зЃЧйЗПпЉМињЩе∞±еПѓдї•еПЧзЫКдЇОеєґи°МеЩ®дїґзЪДйЂШеЇ¶еєґи°МеК†йАЯеКЯиГљпЉМдЊЛе¶ВCPUгАБGPUгАБFPGAз≠ЙеЩ®дїґгАВи¶БеК†йАЯзЪДеКЯиÚ襀зІ∞дЄЇOpenCLеЖЕж†ЄгАВйЗЗзФ®ж†ЗеЗЖCзЉЦеЖЩињЩдЇЫеЖЕж†ЄпЉЫдљЖжШѓпЉМйЗЗзФ®зїУжЮДеѓєеЕґињЫи°Мж≥®йЗКпЉМдї•иЃЊеЃЪеєґи°Ме§ДзРЖжУНдљЬеТМе≠ШеВ®еЩ®з≠ЙзЇІгАВеЫЊ5дЄ≠зЪДдЊЛе≠РеѓєдЄ§дЄ™жХ∞зїДaеТМbињЫи°МзЯҐйЗПеК†ж≥ХпЉМе∞ЖзїУжЮЬеЖЩеЫЮиЊУеЗЇжХ∞зїДеЇФз≠ФдЄ≠гАВзЯҐйЗПзЪДжѓПдЄАеЕГзі†йГљйЗЗзФ®дЇЖеєґи°МзЇњз®ЛпЉМељУйЗЗзФ®еГПFPGAињЩз±їеЕЈжЬЙе§ІйЗПз≤ЊзїЖз≤ТеЇ¶еєґи°МеНХеЕГзЪДеЩ®дїґињЫи°МеК†йАЯжЧґпЉМиГље§ЯеЊИењЂзЪДиЃ°зЃЧеЗЇзїУжЮЬгАВдЄїз®ЛеЇПдљњзФ®ж†ЗеЗЖOpenCLеЇФзФ®з®ЛеЇПжО•еП£(API)пЉМжФѓжМБе∞ЖжХ∞жНЃдЉ†йАБиЗ≥FPGAпЉМи∞ГзФ®FPGAеЖЕж†ЄпЉМдЉ†еЫЮеЊЧеИ∞зЪДжХ∞жНЃгАВ

1KhronosйЫЖеЫҐзљСзЂЩ(www.khronos.org/opencl/)еѓєOpenCLж†ЗеЗЖињЫи°МдЇЖиѓ¶зїЖзЪДдїЛзїНгАВ

дЄОCPUеТМGPUдЄНеРМпЉМеЕґеєґи°МзЇњз®ЛеПѓдї•еЬ®дЄНеРМзЪДеЖЕж†ЄдЄ≠жЙІи°МпЉМиАМFPGAиГље§ЯжПРдЊЫдЄНеРМзЪДз≠ЦзХ•гАВеПѓдї•жККеЖЕж†ЄеКЯиГљдЉ†йАБеИ∞дЄУзФ®жЈ±еЇ¶жµБж∞ізЇњз°ђдїґзФµиЈѓдЄ≠пЉМеЃГдљњзФ®дЇЖжµБж∞ізЇњеєґи°Ме§ДзРЖж¶ВењµпЉМеЬ®жЬђиі®дЄКе∞±жШѓе§ЪзЇњз®ЛзЪДгАВињЩдЇЫжµБж∞ізЇњзЪДжѓПдЄАжЭ°йГљеПѓдї•е§НеИґе§Ъжђ°пЉМдЄОдЄАжЭ°жµБж∞ізЇњзЫЄжѓФпЉМжПРдЊЫжЫіеЉЇзЪДеєґи°Ме§ДзРЖеКЯиГљгАВе¶ВеЫЊ5жЙАз§ЇпЉМеПѓдї•йАЪињЗзЇІиБФеКЯиГљеНХеЕГеЃЮзО∞зЯҐйЗПеК†ж≥ХеЖЕж†ЄпЉМеЬ®OpenCLжППињ∞дЄ≠еЃЮзО∞жѓПдЄАжУНдљЬпЉМињЫи°Ме§НеИґдї•жї°иґ≥еЃЮйЩЕеЇФзФ®зЪДеРЮеРРйЗПеТМеїґжЧґи¶Бж±ВгАВ

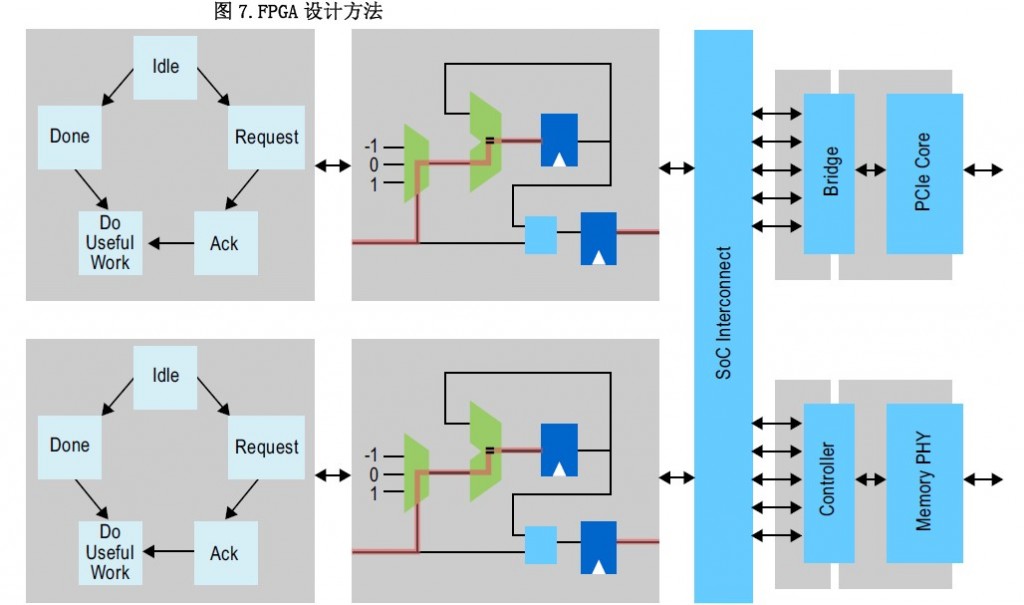

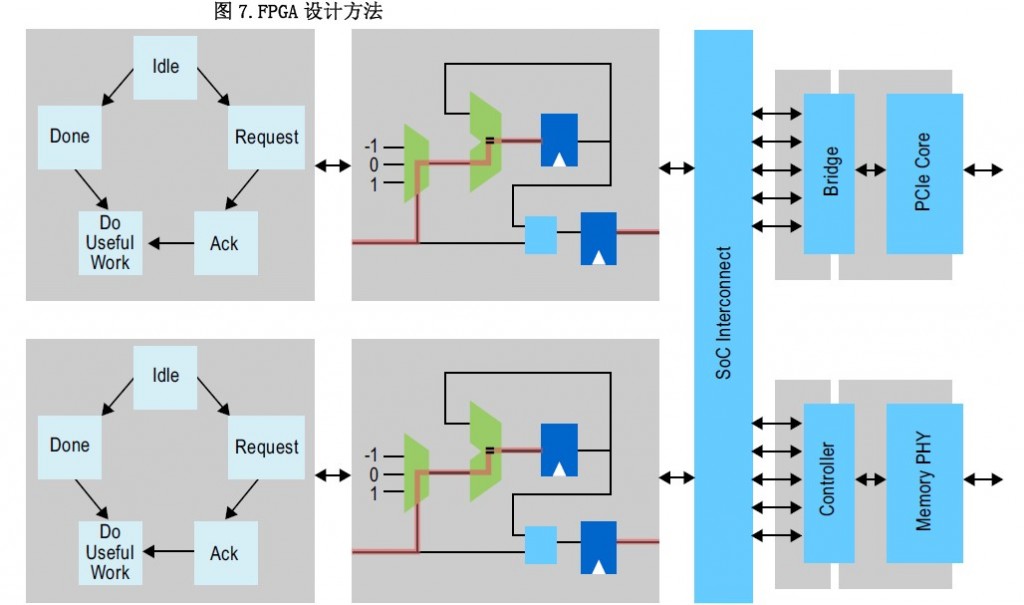

иЩљзДґжЙАжШЊз§ЇзЪДеП™жШѓдЄАдЄ™зЃАеНХи°®еЊБпЉМдљЖжѓПдЄ™еКЯиГљеНХеЕГйГљеПѓдї•жШѓжЈ±еЇ¶жµБж∞ізЇњпЉМдї•дњЭиѓБжЬАзїИзФµиЈѓзЪДеЈ•дљЬйҐСзОЗиґ≥е§ЯйЂШгАВж≠§е§ЦпЉМзЉЦиѓСеЩ®еПѓдї•еїЇзЂЛзФµиЈѓжЭ•зЃ°зРЖдЄОе§ЦйГ®з≥їзїЯзЪДйАЪдњ°гАВеЬ®ињЩдЄ™дЊЛе≠РдЄ≠пЉМDDRxжОІеИґеЩ®еТМPHYињЮжО•иЗ≥еЖЕж†ЄпЉМдљњеЕґиГље§ЯйЂШжХИиЃњйЧЃзЙЗе§ЦйШµеИЧгАВз±їдЉЉзЪДпЉМPCI Express?(PCIe?)IPиЗ™еК®дЊЛеМЦпЉМињЮжО•иЗ≥еЖЕж†ЄпЉМињЩж†ЈпЉМx86дЄїжЬЇиГље§ЯйАЪињЗOpenCLAPIдЄОFPGAеК†йАЯеЩ®ињЫи°МйАЪдњ°гАВ

еЬ®FPGAдЄКеЃЮзО∞OpenCLж†ЗеЗЖзЪДдЉШеКњ

дљњзФ®OpenCLжППињ∞жЭ•еЉАеПСFPGAиЃЊиЃ°пЉМдЄОеЯЇдЇОHDLиЃЊиЃ°зЪДдЉ†зїЯжЦєж≥ХзЫЄжѓФпЉМеЕЈжЬЙеЊИе§ЪдЉШеКњгАВжЬАжШЊиСЧзЪДдЉШеКње¶ВеЫЊ6жЙАз§ЇгАВеЉАеПСиљѓдїґеПѓзЉЦз®ЛеЩ®дїґзЪДжµБз®ЛдЄАиИђеМЕжЛђињЫи°МжЮДжАЭгАБеЬ®Cз≠ЙйЂШзЇІиѓ≠и®АдЄ≠еѓєзЃЧж≥ХзЉЦз®ЛпЉМзДґеРОдљњзФ®иЗ™еК®зЉЦиѓСеЩ®жЭ•еїЇзЂЛжМЗдї§жµБгАВ

ињЩдЄАжЦєж≥ХеПѓдї•дЄОдЉ†зїЯеЯЇдЇОFPGAзЪДиЃЊиЃ°жЦєж≥ХзЫЄжѓФгАВињЩйЗМпЉМиЃЊиЃ°дЇЇеСШзЪДдЄїи¶БеЈ•дљЬжШѓеѓєз°ђдїґжМЙзЕІжѓПдЄ™еС®жЬЯињЫи°МжППињ∞пЉМзФ®дЇОеЃЮзО∞еЕґзЃЧж≥ХгАВдЉ†зїЯжµБз®ЛжґЙеПКеИ∞еїЇзЂЛжХ∞жНЃйАЪиЈѓпЉМе¶ВеЫЊ7жЙАз§ЇпЉМйАЪињЗзКґжАБжЬЇжЭ•жОІеИґињЩдЇЫжХ∞жНЃйАЪиЈѓпЉМдљњзФ®з≥їзїЯзЇІеЈ•еЕЈ(дЊЛе¶ВпЉМSOPCBuilderгАБPlatformStudio)ињЮжО•иЗ≥еЇХе±ВIPеЖЕж†ЄпЉМзФ±дЇОењЕй°їи¶Бжї°иґ≥е§ЦйГ®жО•еП£еЄ¶жЭ•зЪДзЇ¶жЭЯпЉМеЫ†ж≠§пЉМйЬАи¶Бе§ДзРЖжЧґеЇПжФґжХЫйЧЃйҐШгАВOpenCLзЉЦиѓСеЩ®зЪДзЫЃзЪДжШѓеЄЃеК©иЃЊиЃ°дЇЇеСШиЗ™еК®еЃМжИРжЙАжЬЙињЩдЇЫж≠•й™§пЉМдљњдїЦдїђиГље§ЯйЫЖдЄ≠з≤ЊеКЫеЃЪдєЙзЃЧж≥ХпЉМиАМдЄНжШѓйЗНзВєеЕ≥ж≥®дєПеС≥зЪДз°ђдїґиЃЊиЃ°гАВдї•ињЩзІНжЦєеЉПињЫи°МиЃЊиЃ°пЉМиЃЊиЃ°дЇЇеСШеЊИеЃєжШУзІїж§НеИ∞жЦ∞FPGAпЉМжАІиГљжЫіе•љпЉМеКЯиГљжЫіеЉЇпЉМињЩжШѓеЫ†дЄЇOpenCLзЉЦиѓСеЩ®е∞ЖзЫЄеРМзЪДйЂШзЇІжППињ∞иљђжНҐдЄЇжµБж∞ізЇњпЉМдїОиАМеПСжМ•дЇЖFPGAжЦ∞еЩ®дїґзЪДдЉШеКњгАВ

ж°ИдЊЛпЉЪMonteCarloBlack-ScholesжЦєж≥Х

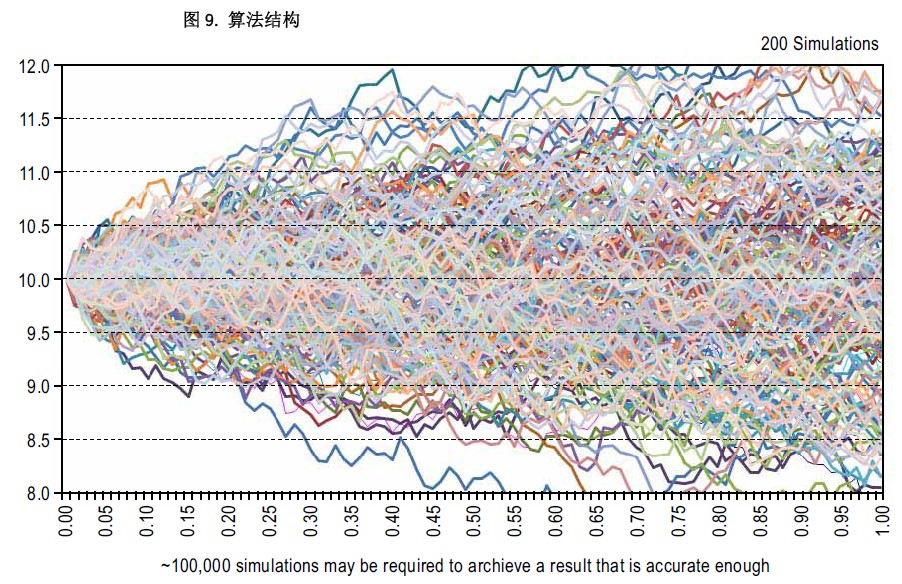

еЬ®йЗСиЮНеЄВеЬЇдЄКжЬАйЗНи¶БзЪДдЄАдЄ™еЯЇеЗЖжµЛиѓХжЦєж≥ХжШѓйАЪињЗMonte Carlo Black-ScholesжЦєж≥ХиЃ°зЃЧжЬЯжЭГдїЈж†ЉгАВиѓ•жЦєж≥ХеЯЇдЇОеѓєеЇХе±ВиВ°з•®дїЈж†ЉзЪДйЪПжЬЇдїњзЬЯпЉМдї•еПКжХ∞зЩЊдЄЗдЄНеРМиЈѓеЊДдЄКзЪДеє≥еЭЗйҐДжЬЯжФґзЫКгАВеЫЊ8дї•еی嚥еМЦзЪДжЦєеЉПжШЊз§ЇдЇЖињЩз±їдїњзЬЯзЪДдЄАдЄ™дЊЛе≠РгАВ

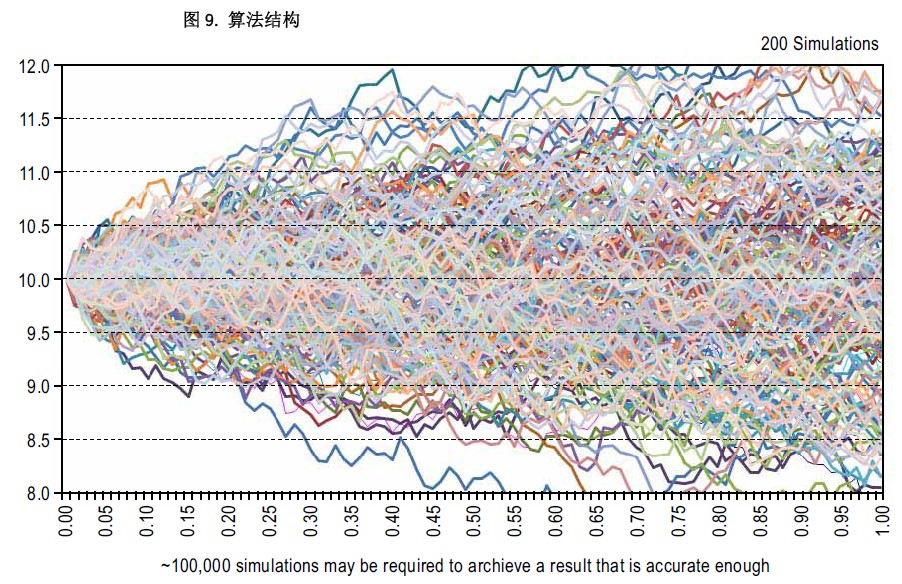

еЫЊ9жШЊз§ЇдЇЖињЫи°МињЩдЄАиЃ°зЃЧзЪДйЂШзЇІзЃЧж≥ХзїУжЮДгАВй¶ЦеЕИйЗЗзФ®MersenneжЧЛиљђйЪПжЬЇжХ∞еПСзФЯеЩ®жЭ•еИЫеїЇеЭЗеМАеИЖеЄГзЪДжХ∞еАЉгАВе∞ЖйЪПжЬЇжХ∞еЇПеИЧйАБеЕ•йАЖж≠£жАБзіѓзІѓеѓЖеЇ¶еЗљжХ∞пЉМдї•дЇІзФЯж≠£жАБеИЖеЄГеЇПеИЧгАВзДґеРОпЉМдљњзФ®еЗ†дљХеЄГжЬЧињРеК®пЉМињЩдЇЫйЪПжЬЇжХ∞зФ®дЇОдїњзЬЯиВ°з•®дїЈж†ЉзЪДеПШеМЦгАВеЬ®жѓПдЄАдїњзЬЯйАЪиЈѓзЪДжЬАеРОпЉМиЃ∞ељХзЬЛжґ®жЬЯжЭГзЪДжФґзЫКпЉМињЫи°Меє≥еЭЗжЭ•дЇІзФЯжФґзЫКйҐДжЬЯеАЉгАВжХідЄ™зЃЧж≥ХйАЪињЗе§ІзЇ¶300и°МзЪДOpenCLдї£з†БжЭ•еЃЮзО∞пЉМеПѓдї•дїОFPGAзІїж§НеИ∞CPUгАБGPUгАВ

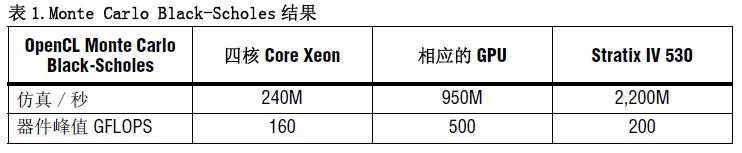

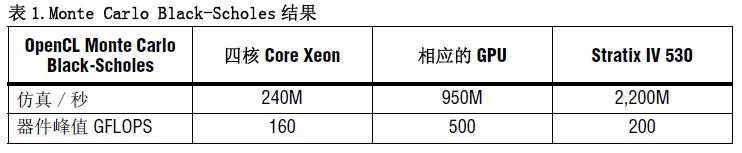

еИ©зФ®йТИеѓєAltera FPGAеЉАеПСзЪДOpenCLеЈ•дљЬеП∞пЉМеПѓдї•дЇІзФЯеЊИе•љзЪДеЯЇеЗЖжµЛиѓХзїУжЮЬпЉМе¶Ви°®1жЙАз§ЇгАВдЄОзЫЄеЇФзЪДGPUзЫЄжѓФпЉМйЭҐеРСStratix? IV FPGA EP4SGX530зЪДOpenCLеЈ•дљЬеП∞еЬ®еРЮеРРйЗПдЄКиґЕињЗдЇЖCPUеТМGPUгАВдЄОзЫЄеЇФзЪДGPUзЫЄжѓФпЉМеЬ®жЙІи°МзЫЄеРМзЪДдї£з†БжЧґпЉМFPGAиІ£еЖ≥жЦєж°ИдЄНдљЖжПРйЂШдЇЖеРЮеРРйЗПпЉМдњЭеЃИдЉ∞иЃ°пЉМеКЯиАЧдєЯеП™жЬЙеЕґдЇФеИЖдєЛдЄАгАВйАЯзОЗеТМйЂШеКЯжХИзЫЄзїУеРИпЉМйЩНдљОдЇЖе§ІиЃ°зЃЧйЗПеЇФзФ®зЪДеКЯиАЧйЬАж±ВгАВ

зїУиЃЇ

еИ©зФ®FPGAдЄКзЪДOpenCLж†ЗеЗЖпЉМдЄОзЫЃеЙНзЪДз°ђдїґдљУз≥їзїУжЮД(CPUгАБGPUпЉМз≠Й)зЫЄжѓФпЉМиГље§Яе§ІеєЕеЇ¶жПРйЂШжАІиГљпЉМеРМжЧґйЩНдљОдЇЖеКЯиАЧгАВж≠§е§ЦпЉМдЄОдљњзФ®VerilogжИЦиАЕVHDLз≠ЙеЇХе±Вз°ђдїґжППињ∞иѓ≠и®А(HDL)зЪДдЉ†зїЯFPGAеЉАеПСжЦєж≥ХзЫЄжѓФпЉМдљњзФ®OpenCLж†ЗеЗЖгАБеЯЇдЇОFPGAзЪДжЈЈеРИз≥їзїЯ(CPU+FPGA)еЕЈжЬЙжШОжШЊзЪДдЇІеУБеПКжЧґйЭҐеЄВдЉШеКњгАВAlteraдЇО2010еєіеК†еЕ•KhronosйЫЖеЫҐпЉМдЄЇж†ЗеЗЖеїЇиЃЊеБЪеЗЇдЇЖзІѓжЮБиі°зМЃгАВ

еИЖдЇЂеИ∞пЉЪ

зЫЄеЕ≥жО®иНР

йЗЗзФ®OpenCL ж†ЗеЗЖеЃЮзО∞FPGA иЃЊиЃ°zip,йЗЗзФ®OpenCL ж†ЗеЗЖеЃЮзО∞FPGA иЃЊиЃ°

йЗЗзФ®OpenCLж†ЗеЗЖеЃЮзО∞FPGAиЃЊиЃ°.pdf

иѓ•иµДжЦЩдЄїи¶БдїЛзїНзФ®openclеЬ®fpgaеє≥еП∞еЉАеПСпЉМеЃЮзО∞еєґи°МеК†йАЯ

OpenCLеЬ®Intel FPGA SDKзЪДдљњзФ®жЦЗж°£пЉМеМЕжЛђеЃЙи£ЕжХЩз®Лдї•еПКеЃЮдЊЛ

еЯЇдЇОOpenCLзЪДFPGAиЃЊиЃ°дЉШеМЦжЦєж≥Хз†Фз©ґ.pdf

intel fpga opencl зЉЦз®ЛжМЗеНЧ The Intel¬Ѓ FPGA SDK for OpenCLвДҐ Programming Guide provides descriptions, recommendations and usage information on the Intel Software Development Kit (SDK) for OpenCL ...

AlteraеЃ£еЄГдЄЪзХМй¶ЦжђЊжФѓжМБFPGAзЪДOpenCLеЈ•еЕЈ.pdf

иµЫзБµжАЭеЕђеПЄзїЩзЪДеЃШжЦєзЪДдї£з†БеЃЮдЊЛпЉМеИЭе≠¶иАЕеПѓдї•дЄЛиљље≠¶дє†пЉМзЖКжЬАзЃАеНХзЪДhellowordз®ЛеЇПеЉАеІЛгАВ

еЯЇдЇОOpenCLзЪДFPGAиЃ°зЃЧз≥їзїЯиЃЊиЃ°жМЗеНЧпЉМSpringerеЗЇзЙИз§Њ2018еєі4жЬИеЗЇзЙИпЉМдїЕдЊЫе≠¶жЬѓдЇ§жµБгАВе¶ВжЬЙдЊµжЭГпЉМеИ†йЩ§гАВ

дїО2011еєіAlteraеЕђеПЄеПСеЄГжФѓжМБеИ©зФ®OpenCLжЭ•еЉАеПСFPGAзЪДSDKеЈ•еЕЈдї•еРОпЉМйЗЗзФ®CPU+FPGAжЮДжИРеЉВжЮДиЃ°зЃЧз≥їзїЯжИРдЄЇеП¶дЄАзІНеЕЈжЬЙзЂЮдЇЙеКЫзЪДиІ£еЖ≥жЦєж°ИгАВжЬђдє¶дЄїи¶БдїЛзїНдЇЖFPGAеЉВжЮДиЃ°зЃЧз≥їзїЯзЪДеЯЇжЬђжЮґжЮДеТМеЉАеПСжЦєж≥ХпЉМеєґдї•е§ЪдЄ™дЄНеРМзЪДж°ИдЊЛдЄЇиѓїиАЕ...

зФ®FPGAжЭ•еК†йАЯйЗЗзФ®OpenCLзЪДе§ЪеКЯиГљжЙУеН∞жЬЇеЫЊеГПе§ДзРЖ

еЯЇдЇОOpenCLеєґи°МеК†йАЯзЃЧж≥Хз†Фз©ґеПКеЕґFPGAеЃЮзО∞пЉИељ≠жЦ∞жШЊпЉЙпЉМеЉВжЮДеєґи°МиЃ°зЃЧзЪДе•љдЄЬи•њ

иѓ¶зїЖжППињ∞дЇЖе¶ВдљХеЬ®дљњзФ®VivadoеЉАеПСзОѓеҐГпЉМеЬ®ZYNQз≥їеИЧFPGAдЄКеЃЮзО∞еЯЇз°АOpenCLзЪДзЉЦз®ЛжµЛиЃЊгАВж≠•й™§жЄЕжЩ∞гАВгАВгАВгАВ

OpenCLйАРж≠•еЃЮзО∞

PipeCNN: An OpenCL-Based Open-Source FPGA Accelerator for Convolution Neural Networks

AlteraеПСеЄГдЄЪзХМзђђдЄАдЄ™йЭҐеРСFPGAзЪДOpenCLиЃ°еИТ.pdf

жСШи¶БпЉЪеЬ®йЂШжАІиГљиЃ°зЃЧгАБе®±дєРеТМзІСе≠¶иЃ°зЃЧеЄВеЬЇпЉМOpenCLзЪДйЗЗзФ®еЬ®жМБзї≠еҐЮйХњгАВOpenCLзЪДзБµжіїжАІеТМдЊњжРЇжАІдљњдєЛжИРдЄЇдЇЖдЄАдЄ™еЉАеПСеЫЊеГПе§ДзРЖеЇФзФ®зЪДеє≥еП∞гАВзДґиАМпЉМOpenCLе∞ЪжЬ™еЇФзФ®еИ∞з°ђжЛЈиіЭжЙУеН∞жЬЇеТМе§ЪеКЯиГљжЙУеН∞жЬЇпЉИMFPпЉЙеЄВеЬЇгАВдЉ†зїЯдЄКпЉМжЙУеН∞жЬЇ/...

еЯЇдЇОOpenCLзЪДCPUж®°еЭЧиЃЊиЃ°дЄОеЃЮзО∞.pdf

openclеЃЮзО∞зЯ©йШµеК†ж≥ХпЉМйЭЮеЄЄйАВеРИеИЭе≠¶иАЕе≠¶дє†дљњзФ®пЉМиГље§ЯеЕ®йЭҐдЇЖиІ£OpenCLзЪДињРи°МеОЯзРЖпЉМжЬђеЃЮй™МзОѓеҐГubuntu+NVIDIA CUDA8.0пЉМеЕ≥дЇОзОѓеҐГйЕНзљЃеПѓдї•жЯ•зЬЛжИСзЪДеНЪжЦЗгАВ

OpenCLйҐЖеЯЯеЕђиЃ§зЪДжЭГе®БиСЧдљЬпЉМзФ±OpenCLж†ЄењГиЃЊиЃ°дЇЇеСШдЇ≤иЗ™жЙІзђФпЉМдЄНдїЕеЕ®йЭҐиАМжЈ±еИїеЬ∞иІ£иѓїдЇЖOpenCLиІДиМГеТМзЉЦз®Лж®°еЮЛпЉМиАМдЄФйАЪињЗе§ІйЗПж°ИдЊЛеТМдї£з†БжЉФз§ЇдЇЖ еЯЇдЇОOpenCLзЉЦеЖЩеєґи°Мз®ЛеЇПеТМеЃЮзО∞еРДзІНеєґи°МзЃЧж≥ХзЪДеОЯзРЖгАБжЦєж≥ХгАБжµБз®ЛеТМжЬАдљ≥еЃЮ иЈµпЉМ...